MIPS Processor Simulation

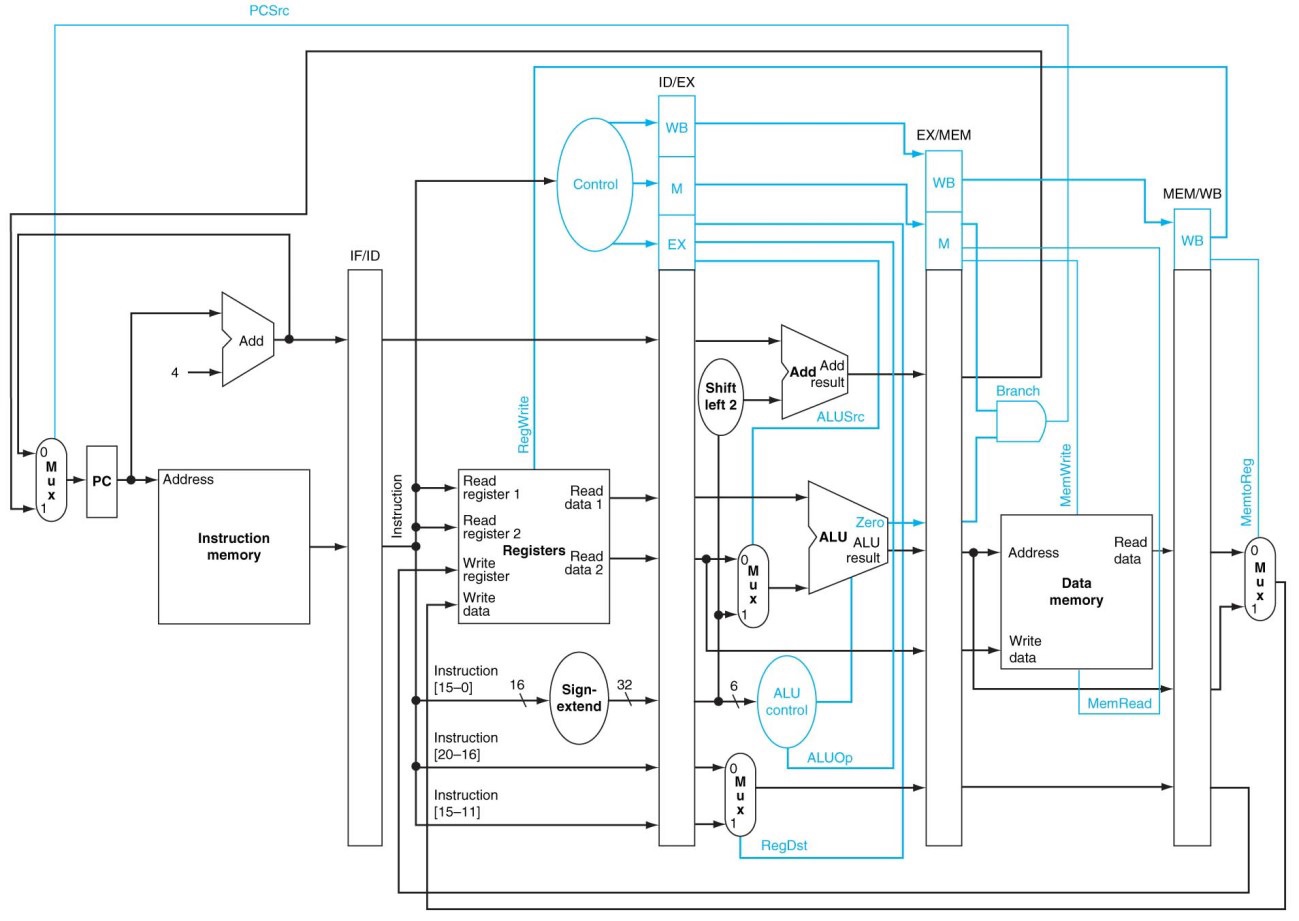

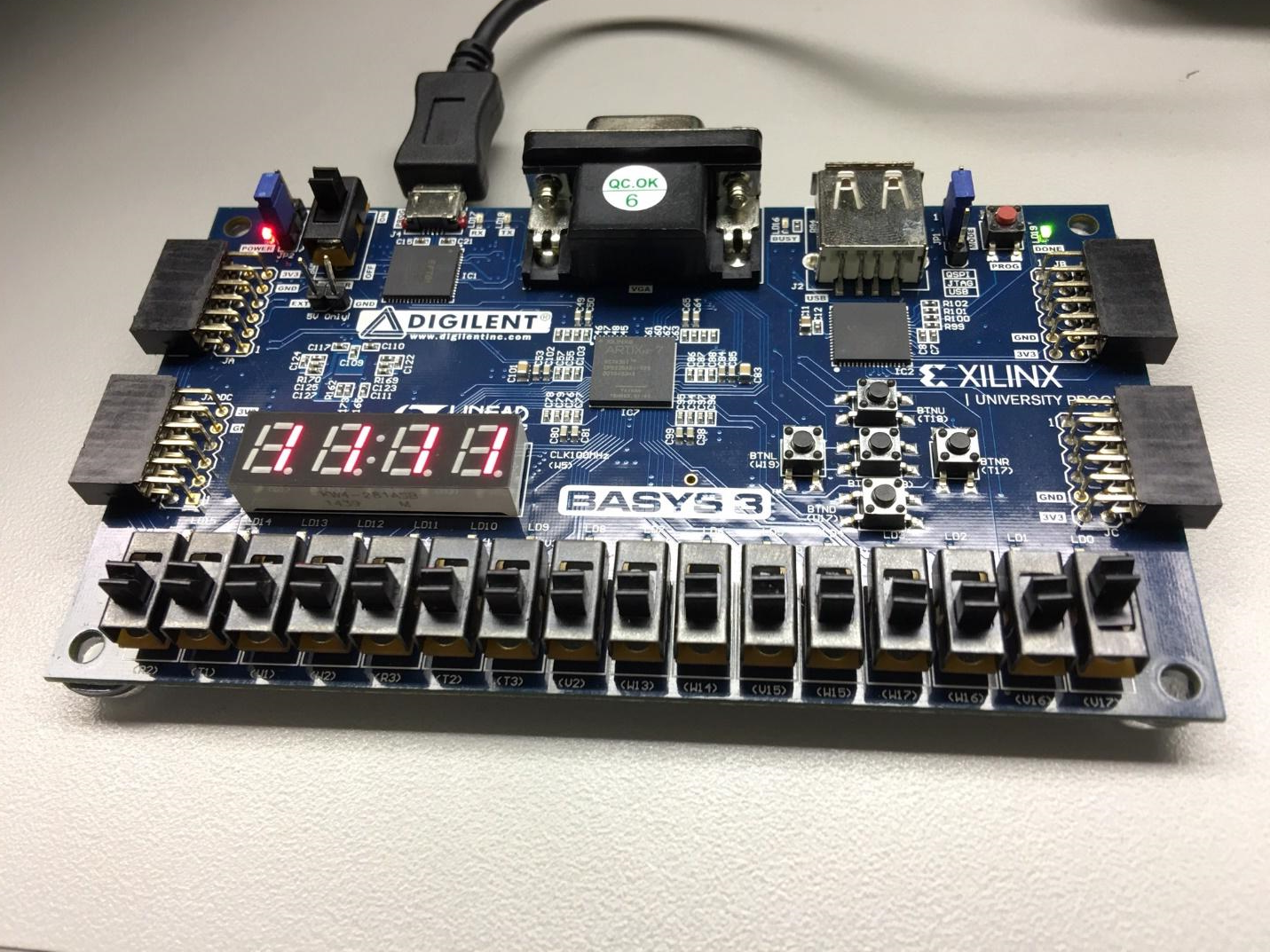

Microprocessor without Interlocked Pipeline Stages, better known as MIPS, is a computer instruction set architecture with relatively simple instructions. A processor for MIPS instructions was simulated and implemented on a Field Programmable Gate Array (FPGA) in EE 361 during Fall 2015.

The simulations were done in Verilog a hardware description language (HDL). The Vivado IDE was used to code the simulations as well as debug them. Furthermore, Vivado was also used to program the FPGA as the simulated processor.

This project provided me with experience for both Verilog and the Vivado IDE. Additionally, it allowed me to gain a better understanding of how MIPS processors work and how instructions are executed by computers. Overall, the project really gave me a better understanding of how computer hardware works and how software is actually run on a processor.